AMD wypuściło CPU Ryzen 70003D pod koniec zeszłego miesiąca i te spotkały się z ciepłym przyjęciem recenzentów i graczy, głównie za sprawą drugiej generacji technologii 3D V-Cache. Teraz producent podzielił się szczegółami technicznymi, które wyjaśniają co nowego przynosi druga generacja pamięci podręcznej układanej w stosy.

AMD zaczęło mieszać litografie w 2019 roku, kiedy użyło 7 nm dla CCD i 12 nm dla matrycy IO w mikroarchitekturze Zen 2. Producent niedawno potwierdził Tom's Hardware, że CPU Zen 4 korzystają z trzech litografii: 5 nm dla CCD, 6 nm dla matrycy IO i 7 nm dla V-Cache.

Podczas prezentacji na konferencji ISSCC AMD wyjaśniło niektóre wyzwania, przed którymi stanęło, układając na sobie elementy produkowane w różnych procesach technologicznych.

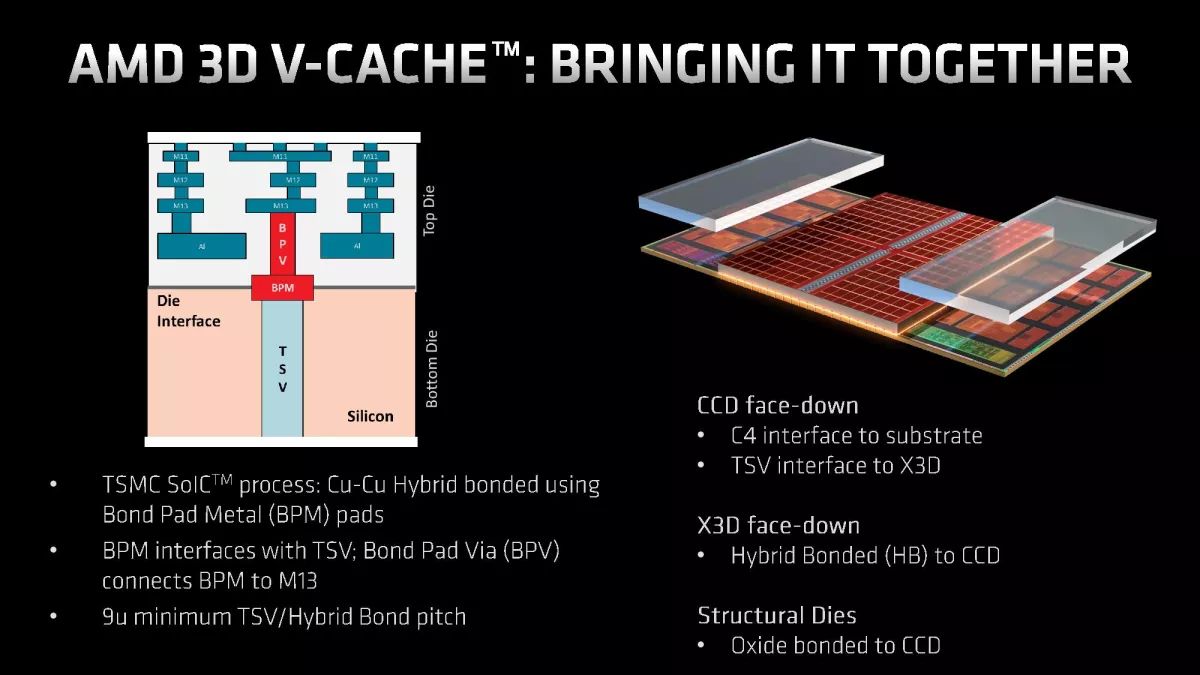

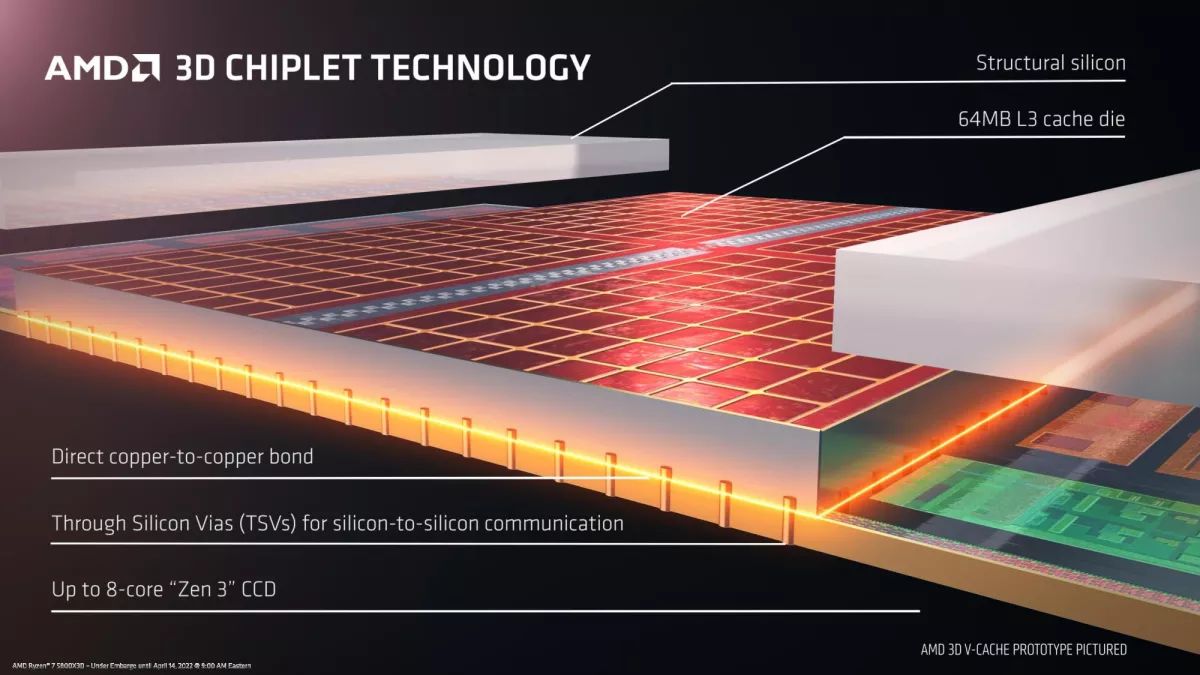

Podczas prezentacji na konferencji ISSCC AMD wyjaśniło niektóre wyzwania, przed którymi stanęło, układając na sobie elementy produkowane w różnych procesach technologicznych. Zarówno model Ryzen 9 7950X3D, jak i Ryzen 7 5800X3D, który jako pierwszy wykorzystywał 3D V-Cache, mają swoje pamięci podręczne V-Cache umieszczone nad zwykłymi pamięciami podręcznymi L3, co umożliwia ich połączenie. Taki układ utrzymuje również V-Cache z dala od ciepła wytwarzanego przez rdzenie. Jednak chociaż pamięć podręczna V-Cache idealnie pasuje do pamięci podręcznej L3 w Ryzenie 7 5800X3D, to w Ryzenie 7950X3D zachodzi z pamięciami podręcznymi L2 na krawędzie rdzeni.

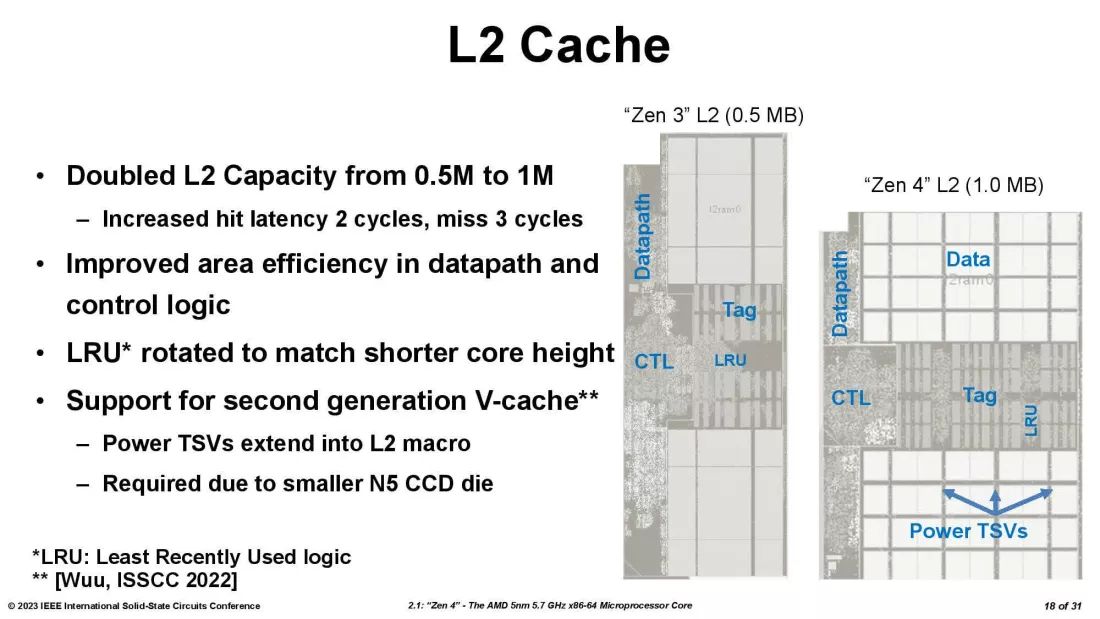

Część problemu wynika z faktu, że AMD podwoiło ilość pamięci podręcznej L2 w każdym rdzeniu z 0,5 MB w Zen 3 do 1 MB w Zen 4. Udało się jednak obejść dodatkowe ograniczenia przestrzenne, robiąc dziury w pamięciach podręcznych L2 dla połączeń through-silicon via (TSV), które dostarczają zasilanie do V-Cache. Sygnały TSV nadal pochodzą z kontrolera w centrum CCD, ale AMD również je zmodyfikowało, aby zmniejszyć ich powierzchnię o 50%.

AMD zmniejszyło V-Cache z 41 mm2 do 36 mm2, ale zachowało tę samą liczbę tranzystorów (4,7 mld). TSMC produkuje pamięć podręczną w nowej wersji 7 nm litografii, którą opracowało specjalnie dla SRAM. W rezultacie pamięć podręczna V-Cache ma o 32% więcej tranzystorów na milimetr kwadratowy niż matryca CCD, mimo że ta została wyprodukowana w znacznie mniejszej 5 nm litografii.

Wszystkie ulepszenia i obejścia zastosowane przez AMD dają w sumie 25% wzrost przepustowości do 2,5 TB/s i przekładają się na bliżej nieokreślony wzrost wydajności. Trzeba przyznać, że jak na 9 miesięcy, jakie dzieli pierwszą i drugą generację 3D V-Cache, AMD udało się dokonać naprawdę dużego postępu.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

AMD tłumaczy, jak poprawiło drugą generację 3D V-Cache