Oprócz nowego przecieku odnośnie procesorów Ryzen 8000 w sieci pojawiły się również informacje dotyczące serwerowych CPU AMD EPYC Turin, a konkretnie Turin-X i Turin Dense.

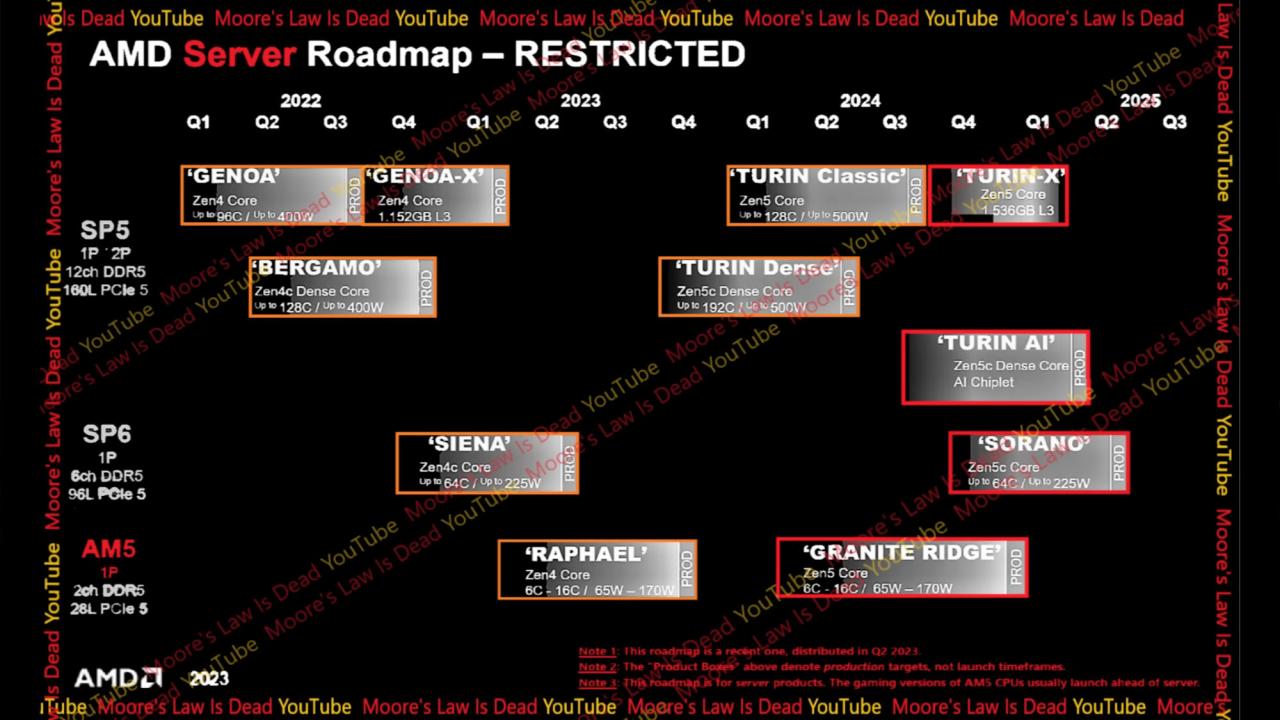

Źródłem ponownie jest Moore’s Law is Dead i youtuber zaprezentował najnowszy harmonogram AMD, dotyczący rodziny procesorów EPYC nowej generacji. Plan obejmuje co najmniej pięć serii procesorów EPYC, których można się spodziewać w latach 2024-2025. AMD potwierdziło już, że Turin to nowa generacja układów EPYC i będzie wykorzystywać zarówno rdzenie Zen 5, jak i Zen 5C,

AMD EPYC Turin (Classic)

Tak więc najpierw otrzymamy procesory AMD EPYC Turin (Classic), które będą trzymały się projektu chipletu i pomieszczą do 128 rdzeni, 256 wątków, a ich TDP wynosić będzie do 500 W, ale w niektórych jednostkach można będzie je skonfigurować do 600 W (jak ujawnione w wycieku harmonogramu Gigabyte). W poprzednim przecieku potwierdzono zaś, że chipy EPYC Turin będą miały tę samą pamięć podręczną L2 i L3, co Zen 4, z niewielkim ulepszeniem pamięci podręcznej L1.

Plan obejmuje co najmniej pięć serii procesorów EPYC, których można się spodziewać w latach 2024-2025.

Główna zmiana nastąpi w sposobie, w jaki AMD organizuje pamięć podręczną w układach Zen 5, które mają wykorzystywać hierarchię „Ladder”. Chipy mają wejść do produkcji w pierwszym kwartale 2024 roku i będą wykorzystywać 4 nm litografię TSMC. Premiera ma nastąpić w trzecim kwartale 2024 roku.

AMD EPYC Turin-X

Procesory AMD EPYC Turin-X, które z kolei będą wyposażone w pamięć podręczną 3D V-Cache. Układy te zachowają 64 MB 3D V-Cache na CCD, co daje łącznie 1024 MB na 16 CCD i 512 MB standardowej pamięci podręcznej L3. W sumie do 1536 MB lub 1,5 GB pamięci podręcznej L3. Jeśli połączymy to z pamięcią podręczną L2 (1 MB na rdzeń) daje to do 1664 MB całkowitej pamięci podręcznej i to bez uwzględnienia pamięci podręcznej L1. To o 33% większy cache w porównaniu z nadchodzącą rodziną procesorów Genoa-X.

AMD EPYC Turin Dense

Przechodząc do Zen 5C, tego typu rdzenie wykorzystają układy EPYC Turin Dense, które zastąpią Bergamo. TurinDense nie jest na razie oficjalną nazwą, ale oczekuje się, że będzie wykorzystywać 3 nm rdzenie Zen 5C, a topowy CPU otrzymać ma do 912 rdzeni. Układy te będą charakteryzować się TDP do 500 W, ale najciekawsze jest to, że mają trafić do produkcji przed standardowymi układami z Turyn. MLID twierdzi, że jest to spowodowane tym, że AMD chce szybciej dostarczyć odpowiedź na 144-rdzeniowe chipy Sierra Forest od Intela, które również spodziewane są w pierwszej połowie 2024 roku.

Oczekiwać mamy jeszcze jednych chipów Turin Dense, znanych jako Turin AI, które mają zawierać te same rdzenie Zen 5C, ale z chipletem AI. Nie ma wielu szczegółów dotyczących tej konkretnej jednostki, ale możemy spodziewać się, że Xilinx IP będzie zasilać chiplet AI dla wybranych aplikacji. AMD, podobnie jak większość firm technologicznych obecnie, nadaje priorytet technologii sztucznej inteligencji.

AMD EPYC Siena

Przecieki wspominają też o następcy procesorów AMD Siena, znanych jako Sorano. Linia AMD EPYC 8004 „Siena” wykorzystuje rdzenie Zen 4/4C na popularniejszej, tańszej platformie o niższej mocy, znanej jako SP6. Obsługuje 6-kanałową pamięć i 96 połączeń PCIe 5.0. Układy te zachowają do 64 rdzeni i TDP na poziomie 225 W, a ich produkcja spodziewana jest w drugiej połowie 2024 r., ale na premierę poczekamy podobno do 2025 r.

Oficjalnych zapowiedzi spodziewać możemy się na wydarzeniu AMD Data Center and AI Technology Premiere, które planowane jest w czerwcu.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

EPYC Turin - nowe serwerowe procesory AMD mogą pozamiatać