Gdy debata o niezależności technologicznej koncentruje się głównie na działaniach podejmowanych w Chiny, bez dużego rozgłosu toczy się konsekwentna praca europejskich zespołów badawczych. Teraz Barcelona Supercomputing Center informuje o przejściu z projektów na ekranach symulatorów do realnego układu scalonego. Instytut, działający poprzez Barcelona Zettascale Lab, uruchomił testowy chip RISC-V wykonany w litografii Intel 3.

Dla środowiska HPC to sygnał, że program budowy kompetencji projektowych na Starym Kontynencie nabiera fizycznego wymiaru. Prototypy przestają być jedynie obietnicą, zaczynają funkcjonować w laboratoriach, pod obciążeniem, z systemem operacyjnym i narzędziami deweloperskimi.

🔥BSC advances European technological sovereignty as 𝗖𝗶𝗻𝗰𝗼 𝗥𝗮𝗻𝗰𝗵 𝗧𝗖1 𝗰𝗵𝗶𝗽 passes validation.

— BSC-CNS (@BSC_CNS) February 9, 2026

💻Tests confirm the robustness of the new #opensource #chip architecture, positioning the Barcelona Zettascale Lab (BZL), led by BSC, among Europe’s leaders in advanced… pic.twitter.com/smTxXylb08

TC1 trafia na płytę

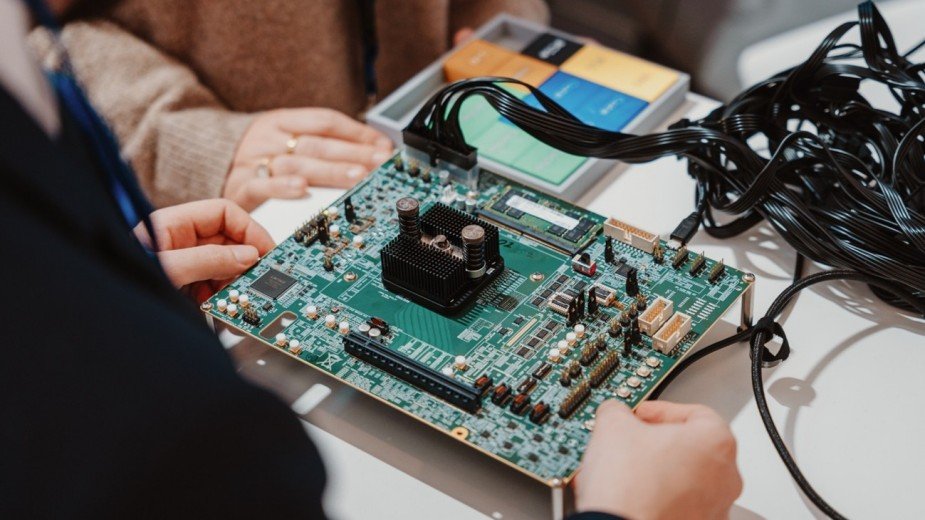

Układ nosi wewnętrzne oznaczenie TC1. Do pierwszych prób wykorzystano platformę Intel Hawk Canyon V2, która umożliwiła szybkie sprawdzenie komunikacji z pamięcią i urządzeniami peryferyjnymi. Projekt wpisuje się w działania prowadzone w ramach European Processor Initiative, programu mającego dostarczyć procesory do przyszłych europejskich superkomputerów oraz systemów przemysłowych.

TC1 wykorzystuje podejście heterogeniczne. W strukturze znalazły się trzy moduły zbudowane wokół różnych rdzeni RISC-V, nazwanych Sargantana, Lagarto Ka oraz Lagarto Ox. Każdy z nich odpowiada za inny profil zadań, od obliczeń ogólnego przeznaczenia po operacje wektorowe. Sam podsystem CPU zajmuje niewielką część matrycy, resztę wypełniają szybkie interfejsy, w tym PCIe Gen5 i DDR5.

Skala integracji robi wrażenie szczególnie w zestawieniu z dużymi chipletami stosowanymi w procesorach serwerowych i desktopowych. Europejski projekt pokazuje, że nawet niewielka powierzchnia może pomieścić pełny zestaw funkcjonalności potrzebnych do badań nad kolejnymi generacjami architektur.

Droga do krzemu

Na wczesnym etapie prac technologia Intel 3 pozostawała poza zasięgiem zewnętrznych zespołów. Inżynierowie z Barcelony prowadzili weryfikację RTL z użyciem procesu TSMC N7 jako zastępczego środowiska produkcyjnego. Dopiero później projekt trafił do fabryk Intela.

Po otrzymaniu gotowych próbek rozpoczął się etap uruchamiania systemu operacyjnego. W maju 2025 roku na chipie wystartował Linux, najpierw w obecności partnera produkcyjnego, później już samodzielnie w laboratoriach BSC. Kolejna partia pięciuset egzemplarzy pozwoliła na szeroką walidację funkcjonalną. Większość sztuk aktywowała komplet trzech rdzeni, a pomiary wskazały częstotliwości sięgające 1,25 GHz.

Nowoczesny, nie demonstracyjny

Intel 3 należy do generacji procesów litograficznych wykorzystujących EUV. W hierarchii producenta istnieją już bardziej zaawansowane rozwiązania, jednak użyty w projekcie proces reprezentuje klasę, w której powstaje wiele współczesnych układów logicznych. Dla europejskich partnerów najistotniejsze było potwierdzenie zdolności przeniesienia własnych projektów na aktualną technologię przemysłową.

RISC-V rozwijany w Barcelonie nie ma ambicji rywalizacji z topowymi konstrukcjami x86 czy ARM w komputerach konsumenckich. Priorytet stanowi zbudowanie łańcucha kompetencji od projektu architektury, przez narzędzia, po fizyczny krzem gotowy do integracji w przyszłych maszynach obliczeniowych.

Namacalny krok ku autonomii

Dla Europy udany start TC1 jest dowodem postępu w kierunku większej samodzielności w obszarze wysokowydajnych obliczeń. Dla Intela to potwierdzenie możliwości współpracy z wymagającymi klientami nad złożonymi projektami. Pojedynczy prototyp nie zmienia układu sił na rynku procesorów, lecz pokazuje zdolność do realizacji ambitnych planów i buduje fundament pod kolejne iteracje.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

Europa ma własny procesor RISC-V. Za produkcję odpowiada Intel