Dyrektor generalny Intela, Pat Gelsinger, podczas sesji pytań i odpowiedzi pierwszego dnia konferencji Innovation 2023, potwierdził, że firma opracowuje technologię pamięci podręcznej układanej w stosy 3D dla swoich procesorów.

Technologia ta polega na rozszerzeniu wbudowanej pamięci podręcznej ostatniego poziomu (cache L3) procesora o dodatkową pamięć SRAM, fizycznie ułożoną na wierzchu i połączoną z szerokopasmową siecią danych pamięci podręcznej. Pamięć cache układana w stosy działa z tą samą szybkością, co pamięć podręczna na matrycy, dlatego łączny rozmiar pamięci podręcznej jest widoczny dla oprogramowania jako pojedynczy, ciągły adresowalny blok pamięci cache.

Pat Gelsinger potwierdził, że Intel opracowuje technologię pamięci podręcznej układanej w stosy 3D dla swoich procesorów.

AMD i 3D V-Cache

AMD wykorzystało pamięć podręczną ze stosami 3D w swoich CPU do różnych zastosowań. W procesorach konsumenckich, takich jak seria Ryzen X3D, pamięć podręczna zapewnia znaczny wzrost wydajności w grach, ponieważ większa pamięć podręczna L3 sprawia, że więcej danych renderowania gry jest natychmiast dostępnych dla rdzeni procesora. W przypadku procesorów serwerowych, takich jak EPYC „Milan-X” i „Genoa-X”, dodatkowa pamięć podręczna zapewnia znaczny wzrost obciążeń obliczeniowych intensywnie korzystających z pamięci.

Intel nieco inaczej podchodzi do tematu

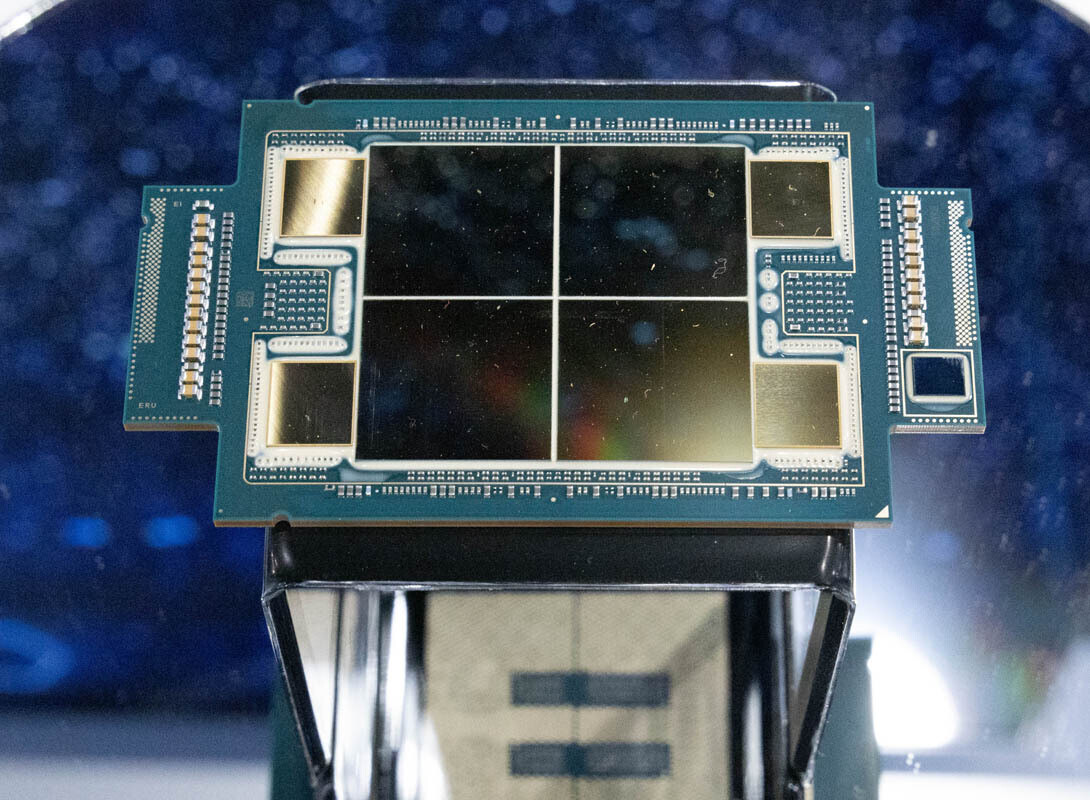

Gelsinger stwierdził w swojej odpowiedzi, że podejście Intela do pamięci podręcznej układanej w stosy 3D będzie inne na poziomie sprzętowym w porównaniu z rozwiązaniem AMD. Technologia Czerwonych została opracowana we współpracy z TSMC i opiera się na technologii pakowania SoIC od tajwańskiego producenta, która umożliwia okablowanie o dużej gęstości pomiędzy matrycą CCD a chipletem pamięci podręcznej. Intel wykorzystuje własne fabryki do produkcji matryc procesorów i będzie musiał używać własnej technologii.

„Kiedy wspominasz o V-Cache, masz na myśli bardzo specyficzną technologię, którą TSMC stosuje również w przypadku niektórych swoich klientów. Oczywiście my robimy to inaczej, prawda? A ten konkretny rodzaj technologii nie jest czymś, co jest częścią Meteor Lake, ale w naszym planie działania widać pomysł krzemu 3D, w którym będziemy mieć pamięć podręczną na jednej kości, a obliczenia procesora będziemy wykonywać na kości ułożonej na wierzchu, i oczywiście korzystając z EMIB i Foveros, będziemy mogli stworzyć różne możliwości” – powiedział Gelsinger.

„Cieszymy się, że mamy zaawansowane możliwości dla architektur pamięci nowej generacji, co pozwoli nam uzyskać przewagę w zakresie układania stosów 3D, zarówno w przypadku małych kości, jak i bardzo dużych pakietów dla sztucznej inteligencji i serwerów o wysokiej wydajności. Mamy więc pełen zakres tych technologii. Będziemy je wykorzystywać w naszych produktach, a także prezentować je klientom Foundry (IFS)” – dodał.

Intel przedstawił niedawno szczegółowe informacje na temat architektury swojego nadchodzącego procesora klienckiego „Meteor Lake”, w którym technologia pakowania Foveros i połączenia między płytkami pozwalają różnym chipletom działać jak spójny krzem. Wydaje się, że Intel rozwiązał problemy z opóźnieniami wynikające z umieszczenia iGPU, rdzeni procesora i kontrolerów pamięci na oddzielnych płytkach.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

Intel idzie śladami AMD i także będzie układać pamięć cache w stosy 3D