W sieci pojawia się coraz więcej przecieków na temat kolejnej architektury CPU od AMD i najnowsze ujawniają, że Zen 5 otrzyma w pełni przeprojektowaną pamięć podręczną, która pomoże zwiększyć IPC (liczba operacji na sekundę) w procesorach nowej generacji.

Źródłem tych informacji jest AdoredTV, które ma niezłą historię, jeśli chodzi o tego typu przecieki. Architektura Zen 4 jest wciąż relatywnie nowa i AMD zapewne szykuje jeszcze mnóstwo produktów opartych na tej technologii, ale firma podobno ma już pierwsze próbki wczesnych prototypów Zen 5 w swoich laboratoriach.

Prace nad rdzeniową architekturą AMD Zen 5, która nosić ma nazwę kodową „Nirvana”, podobno rozpoczęły się już w latach 2020-2021. Oczekuje się, że pierwsze produkty Zen 5 zadebiutują na rynku 2024 roku i jak wynika z ostatnich przecieków, zostaną stworzone całkowicie od podstaw. Ponieważ jest to całkowicie nowy projekt, wewnętrzna architektura procesora z pewnością ulegnie dużym zmianom, na co właśnie wskazuje AdoredTV.

Zen 5 podobno otrzyma w pełni przeprojektowaną pamięć podręczną, która pomoże zwiększyć IPC.

.jpg?time=1682580523955)

Cache typu drabina

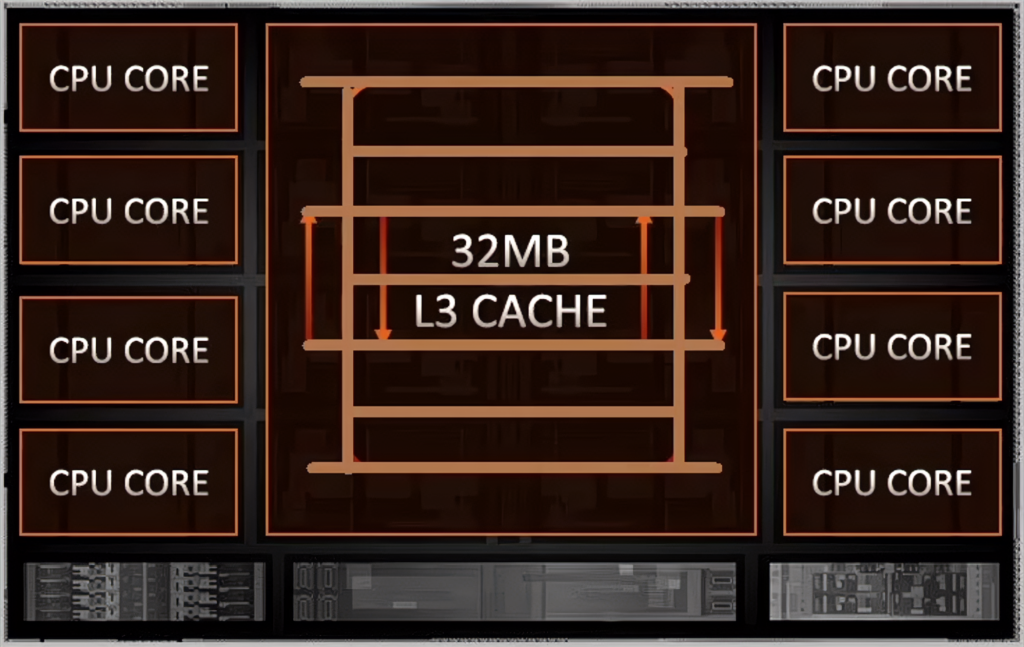

Pierwszą poważną zmianą w architekturze Zen 5 ma być użycie nowej współdzielonej pamięci podręcznej „Ladder”. Wcześniejsze architektury Zen miały pamięć podręczną L3 podzieloną na dwa 16 MB bloki współdzielone przez dwa CCX w każdym CCD. Każdy CCX mógł uzyskać dostęp tylko do 16 MB z puli pamięci podręcznej L3.

Wraz z Zen 3 wprowadzono duże zmiany, bo zrezygnowano z podwójnego CCX na rzecz pojedynczego, który zawierał współdzieloną pulę pamięci podręcznej L3 o pojemności 32 MB. Ta była połączona ze wszystkimi 8 rdzeniami w matrycy w konfiguracji pierścienia. AMD zachowało ten sam projekt w układach Zen 4, ale Zen 5 podobno ponownie wprowadzi duże zmiany w tym zakresie za sprawą 32 MB pamięci podręcznej L3 „Ladder”. Mówi się, że ta struktura drastycznie zmniejsza opóźnienia między rdzeniami i wąskie gardła w komunikacji w porównaniu do połączenia pierścieniowego. Przedstawiona grafika ma jedynie na celu wizualne przedstawienie działania nowej struktury pamięci podręcznej L3 i nie wiadomo, czy pojemność pamięć podręczna L3 utrzyma się na poziomie 32 MB, czy też zostanie zwiększona.

Z najnowszych plotek wynika zaś, że zwiększona zostanie pamięć podręczna L2. AdoredTV twierdzi, powołując się na swoje źródła, że pamięć cache drugiego poziomu dla każdego rdzenia procesora AMD Zen 5 wzrośnie. AMD ma testować w swoich laboratoriach CPU z zarówno 2 MB, jak i 3 MB pamięci podręcznej L2 na rdzeń, ale nie ma pewności, że chodzi tu o Zen 5, jeśli jednak tak jest, oznacza to odpowiednio 2x i 3x wzrost w stosunku do 1 MB pamięci podręcznej na rdzeń dostępnej w rdzeniach Zen 4.

Wzrost IPC

To może bezpośrednio przełożyć się na wzrost IPC i przy 2 MB pamięci podręcznej L2 na rdzeń spodziewać należy się 4% poprawy, a przy 3 MB 7%. Mowa tu o wzroście wydajności w obciążeniach wielowątkowych, bo w scenariuszach jednowątkowych wzrosty IPC mogą być symboliczne.

AMD potwierdziło, że nowa architektura Zen 5 zadebiutuje w 2024 roku. Z dotychczasowych informacji wynika, że procesory bazujące na tej technologii będą dostępne w trzech wariantach: Zen 5, Zen 5 V-Cache i Zen 5c. Te ostatnie (Zen 5c) mają być podobno odpowiedzią AMD na ostatnie CPU Intela i wprowadzą hybrydową konfigurację rdzeni.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

Kolejne przecieki na temat AMD Zen 5 sugerują przeprojektowaną pamięć cache