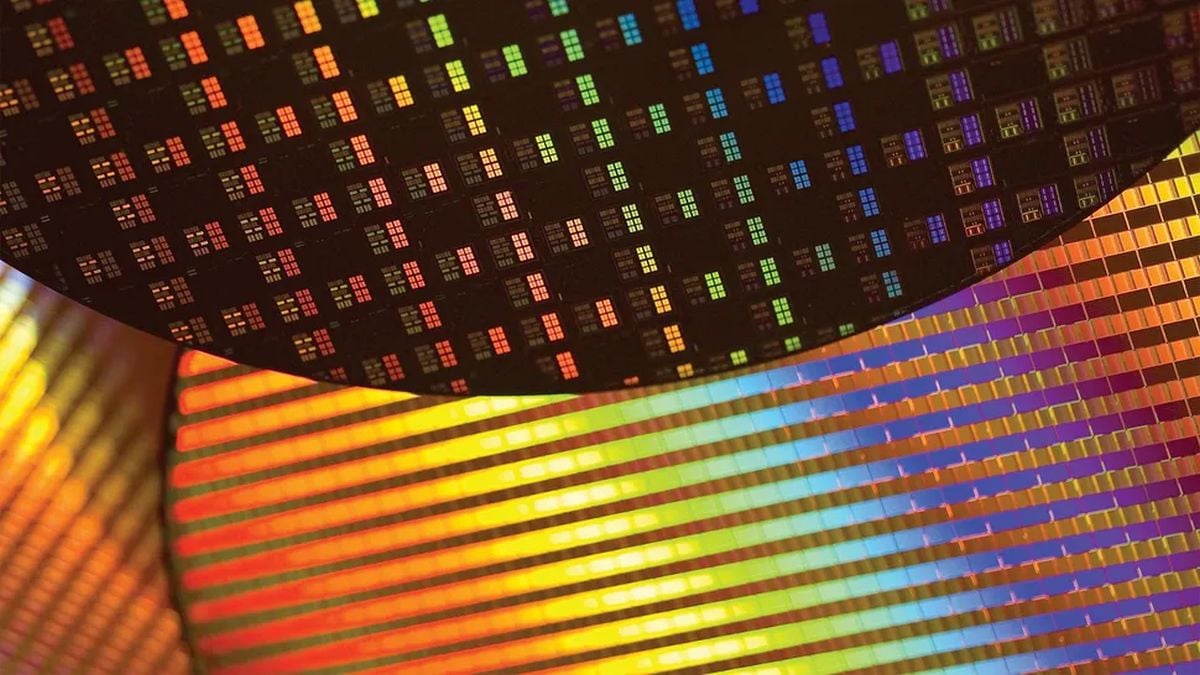

TSMC ogłosiło, że w drugiej połowie 2025 roku rozpocznie masową produkcję półprzewodników przy użyciu procesu technologicznego N2 (klasy 2 nm). Obecnie firma koncentruje się na dopracowywaniu tej nowej technologii, zmniejszając zmienność i gęstość defektów, co pozwoli na poprawę uzysków produkcyjnych.

Według jednego z pracowników TSMC, znanego jako Dr. Kim, poprawa uzysków testowych układów scalonych wyniosła już 6%. Jak podkreślił, oznacza to „oszczędności rzędu miliardów dolarów” dla klientów firmy.

Testy i wyzwania związane z N2

Na tym etapie TSMC testuje układy SRAM i logiczne w technologii 2 nm, ale nie wiadomo, który z tych typów układów skorzystał na poprawie uzysków. Firma planuje rozpoczęcie usług testowych dla klientów dopiero w styczniu 2025 roku, co oznacza, że obecne działania koncentrują się na prototypach, a nie na gotowych projektach układów scalonych.

Poprawa uzysków ma kluczowe znaczenie dla klientów, ponieważ płacą oni za cały wafel krzemowy. Wyższa liczba działających chipów na waflu przekłada się na mniejsze koszty jednostkowe produkcji.

TSMC ogłosiło, że w drugiej połowie 2025 roku rozpocznie masową produkcję półprzewodników przy użyciu procesu technologicznego N2.

GAA: nowa generacja tranzystorów

Proces technologiczny N2 będzie pierwszym w ofercie TSMC, który wykorzysta tranzystory nanoarkuszowe typu Gate-All-Around (GAA). Ta technologia obiecuje znaczne zmniejszenie zużycia energii, poprawę wydajności oraz wyższą gęstość tranzystorów.

W porównaniu z tranzystorami FinFET stosowanymi w procesie N3, GAA zmniejsza wycieki energii dzięki lepszej kontroli elektrostatycznej. Umożliwia też mniejszy rozmiar komórek SRAM przy zachowaniu wysokiej wydajności i pozwala na dalszą miniaturyzację logicznych tranzystorów i komórek SRAM dzięki ulepszonym możliwościom dostrajania napięcia progowego. Mimo tych zalet, produkcja nowego typu tranzystorów będzie wymagała od TSMC minimalizowania wad produkcyjnych w celu uzyskania jak najlepszych uzysków.

Korzyści technologiczne procesu N2

Układy scalone produkowane w procesie N2 mają oferować o 25–30% mniejsze zużycie energii przy tej samej liczbie tranzystorów i częstotliwości pracy w porównaniu do N3E. Oczekiwać mamy również Poprawy wydajności o 10–15% przy zachowaniu tej samej liczby tranzystorów i mocy, a także 15% większą gęstość tranzystorów, co pozwoli na tworzenie mniejszych i bardziej efektywnych układów.

Masowa produkcja układów w technologii N2 ma ruszyć w drugiej połowie 2025 roku, prawdopodobnie w ostatnich miesiącach roku. TSMC ma więc jeszcze dużo czasu, aby udoskonalić proces produkcyjny.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

TSMC poprawia uzysk 2 nm litografii. To miliardy oszczędności dla klientów