Producenci procesorów x86 nie zamierzają bez walki oddać rynku serwerów architekturze ARM, która zyskuje coraz większe uznanie. Intel planuje wypuścić Sierra Forest, wyposażone w dużą liczbę E-rdzeni, podczas gdy AMD pracuje nad Zen 4c, które będzie charakteryzować się "gęstymi" rdzeniami.

Trwa walka z ARM w segmencie serwerów.

Ostatnio architektura ARM zdołała zwiększyć swoją obecność na rynku serwerowym. W dziedzinach takich jak centra danych i chmury, duże ilości rdzeni są istotne, ale sama wydajność nie musi być ekstremalna. W odpowiedzi na to Intel przygotowuje swoje procesory Sierra Forest, które posiadają aż 144 rdzenie, jednak są one oparte wyłącznie na rdzeniach E-Core i nie posiadają Hyper-Threadingu. Jednakże, mają zapewnić solidną wydajność. Z kolei AMD planuje odpowiedzieć za pomocą swojej architektury Zen 4c, znanej także jako Bergamo. Tutaj skupia się się na tworzeniu "gęstych" rdzeni, co pozwoli na umieszczenie znacznie większej liczby rdzeni na mniejszej powierzchni. W rezultacie, procesory AMD będą miały do 128 rdzeni, ale w przeciwieństwie do Intela będą posiadać technologię SMT, umożliwiającą obsługę nawet 256 wątków. Ponadto, procesory AMD będą oferować pełen zestaw instrukcji.

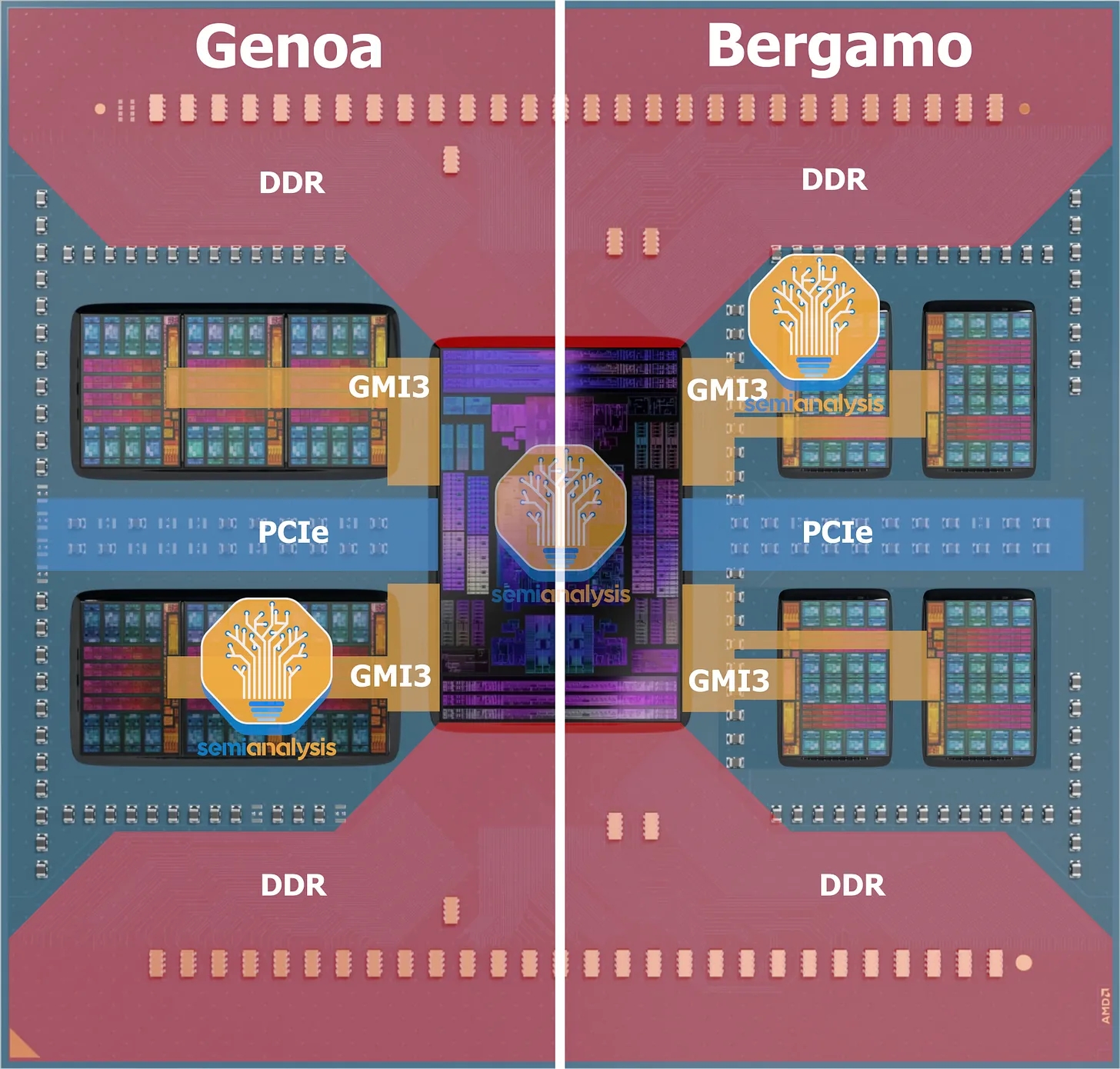

Procesory AMD EPYC Bergamo będą wyposażone w 16 rdzeni Zen 4C na każdym CCD przy 35% mniejszym obszarze rdzenia. Wykorzystają porzuconą wcześniej architekturę dwóch jednostek CCX w jednym CCD.

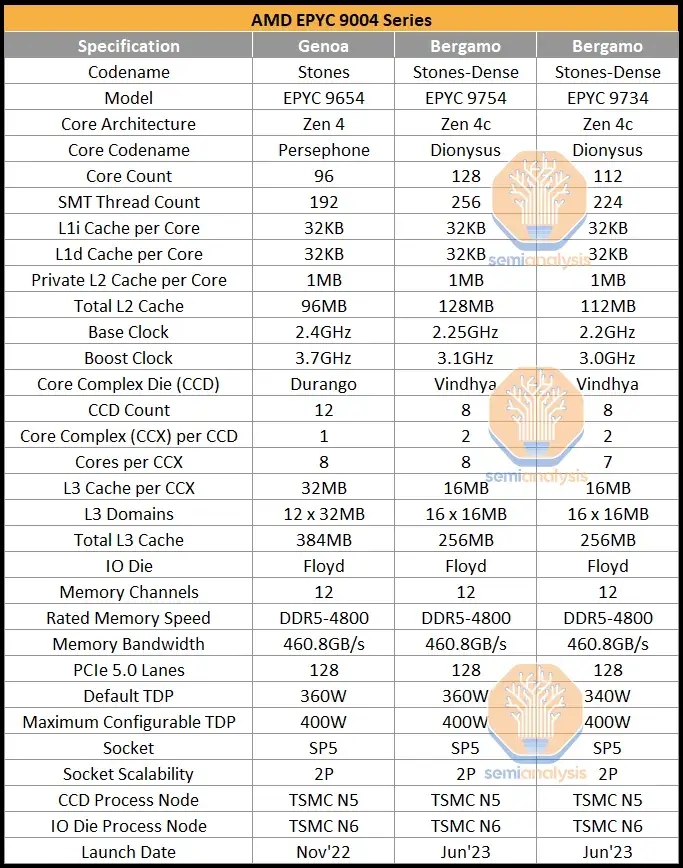

Wiemy już o dwóch procesorach z serii Bergamo, mianowicie EPYC 9734 oraz EPYC 9754. Oba modele są oparte na architekturze Zen 4c i posiadają odpowiednio 112 i 128 rdzeni (co oznacza, że liczba wątków wynosi odpowiednio 224 lub 256). Podobnie jak w przypadku procesorów Genoa z architekturą Zen 4, również tutaj mamy 32 kB pamięci podręcznej instrukcji L1 oraz 32 kB pamięci podręcznej danych L1, a także 1 MB pamięci podręcznej L2 na rdzeń.

Ciekawostką jest fakt, że w procesorach tych zastosowano architekturę, w której jeden CCD zawiera 16 rdzeni, a nie jak obecnie w AMD - 8 rdzeni. Powraca tutaj do użytku porzucona wcześniej architektura dwóch jednostek CCX w jednym CCD. Każde CCX posiada 8 rdzeni (7 rdzeni w przypadku procesora o 112 rdzeniach), a ponieważ w jednym CCD znajdują się dwa CCX, otrzymujemy łącznie 16 rdzeni na jednym CCD. W przypadku procesorów Bergamo mamy łącznie 8 takich CCD, czyli jest ich mniej w porównaniu do modelu EPYC 9654 posiadającego 12 CCD, z każdym zawierającym 8 rdzeni. CCD w procesorze Genoa nosi nazwę Durango, natomiast w Bergamo nazywa się Vindhya.

Przejdźmy teraz do pamięci podręcznej L3. Każde CCX ma 16 MB pamięci podręcznej L3, co daje nam łącznie 32 MB na CCD. Jednakże, pojawia się tu znany problem, polegający na tym, że rdzenie należące do różnych CCX w tym samym CCD nie mają bezpośredniego dostępu do pamięci podręcznej L3, co może prowadzić do spadku wydajności. W przypadku implementacji tych procesorów w środowiskach chmurowych, gdzie zazwyczaj nie ma znaczącego współdzielenia danych między rdzeniami, nie powinno to stanowić większego problemu. Jednak w przypadku zastosowań obliczeniowych lepiej będzie sięgnąć po klasyczną architekturę Zen 4.

16 rdzeni Zen 4c jest niewiele większych niż 8 rdzeni Zen 4

Warto również zauważyć, że podczas gdy 96-rdzeniowy procesor Genoa ma łącznie 384 MB pamięci podręcznej L3 (12 × 32 MB), 128-rdzeniowy procesor Bergamo ma "tylko" 256 MB (8 × 2 × 16 MB). Jeśli chodzi o powierzchnię CCD, klasyczna matryca CCD w architekturze Zen 4 ośmiordzeniowej ma wymiary 66,3 mm², podczas gdy matryca CCD w architekturze Zen 4c o szesnastu rdzeniach jest nieznacznie większa i ma powierzchnię 72,7 mm².

W przypadku procesora Bergamo mamy 12-kanałowy kontroler pamięci DDR5-4800, który zapewnia przepustowość wynoszącą 460,8 GB/s. Liczba 128 linii PCIe 5.0 pozostaje niezmieniona. Podobnie jak w przypadku procesora Genoa, Bergamo będzie kompatybilne z gniazdem SP5 i będzie obsługiwać systemy dwuprocesorowe. Matryca CCD będzie produkowana w procesie TSMC N5, natomiast chiplet IO zostanie wyprodukowany w technologii TSMC N6.

Procesor EPYC 9754 (Bergamo) o liczbie 128 rdzeni powinien mieć takie samo TDP wynoszące 360 W, jak procesor EPYC 9654 (Genua) o liczbie 96 rdzeni. Natomiast procesor EPYC 9734 (Bergamo) o liczbie 112 rdzeni powinien osiągnąć TDP na poziomie 340 W. Jeśli chodzi o częstotliwości, podstawowe wynoszą 2,25 GHz dla wersji 128-rdzeniowej i 2,2 GHz dla wersji 112-rdzeniowej, a częstotliwość Boost wynosi odpowiednio 3,1 GHz i 3,0 GHz. Są one zdecydowanie niższe niż w przypadku procesora Genua, który ma częstotliwość podstawową wynoszącą 2,4 GHz i częstotliwość Boost wynoszącą 3,7 GHz. Wszystkie trzy modele mają jednak możliwość konfiguracji mocy do 400 W. Planuje się, że nowa seria procesorów zostanie zaprezentowana w czerwcu tego roku.

Pokaż / Dodaj komentarze do: Kompaktowy AMD Zen 4c: powrót dwóch CCX w jednym CCD i jeszcze więcej rdzeni...