TSMC podzieliło się najnowszymi informacjami o stanie zaawansowania technologii procesu 2 nm (N2) podczas tegorocznego North American Technology Symposium. Najnowsze dane pokazują, że pomimo fundamentalnej zmiany w architekturze tranzystorów, firma osiąga wyraźnie lepsze rezultaty w zakresie redukcji defektów niż w przypadku wcześniejszych generacji. Wszystko wskazuje na to, że masowa produkcja układów w procesie N2 ruszy zgodnie z planem — pod koniec czwartego kwartału 2025 roku.

Gęstość defektów (oznaczana jako D0) to jeden z kluczowych wskaźników jakości technologii półprzewodnikowej. Określa, ile wad występuje średnio na określonej powierzchni krzemowego wafla. Im mniejsza gęstość defektów, tym większa wydajność produkcji i tym więcej pełnowartościowych chipów trafia z fabryki do klientów. Wraz ze zmniejszaniem się rozmiarów tranzystorów — dziś mierzone już w nanometrach — utrzymanie niskiej gęstości defektów staje się coraz większym wyzwaniem technologicznym.

Nowa architektura, stare mistrzostwo — TSMC z sukcesem wdraża tranzystory GAA

Proces N2 to pierwszy w historii TSMC proces technologiczny, w którym zastosowano tranzystory typu nanosheet z bramką otaczającą kanał (GAAFET, Gate-All-Around Field Effect Transistors), zamiast dotychczasowych FinFET-ów. Pomimo radykalnej zmiany architektury tranzystora, TSMC już teraz notuje niższą gęstość defektów na tym etapie rozwoju niż w przypadku N3, N5 i N7, które opierały się na sprawdzonej technologii FinFET.

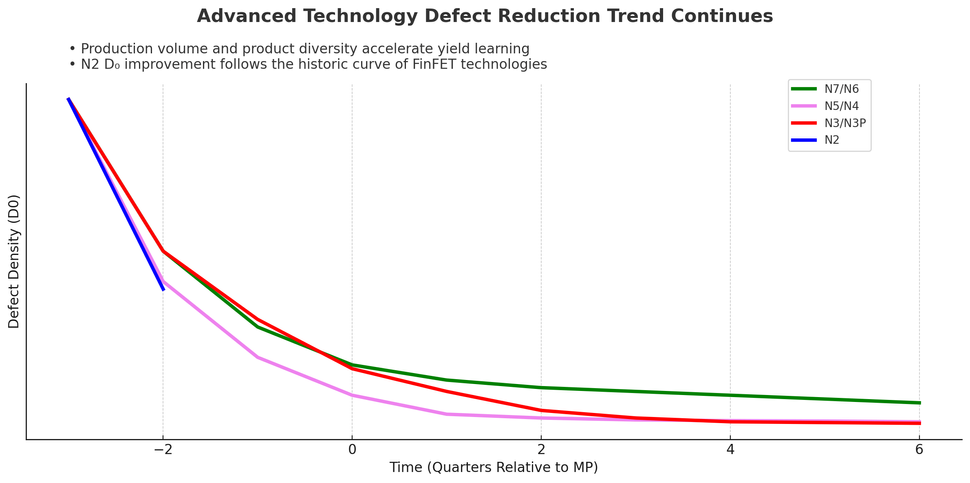

Według zaprezentowanego slajdu, krzywa redukcji defektów dla procesu N2 przebiega stromo i szybko zbliża się do poziomów osiąganych przez dojrzałe już procesy produkcyjne. To oznacza, że TSMC skutecznie zaadaptowało swoją wiedzę o zarządzaniu jakością do nowej klasy tranzystorów — bez wyraźnych opóźnień czy problemów.

Co mówią dane? Analiza krzywych redukcji defektów

Opublikowany wykres porównuje gęstość defektów dla czterech generacji technologii TSMC — od N7/N6 po najnowszy N2 — na przestrzeni od trzech kwartałów przed masową produkcją (MP) do sześciu kwartałów po niej.

-

N7/N6 (zielony) – wykazał najwolniejszą redukcję defektów, z bardziej liniowym trendem poprawy.

-

N5/N4 (fioletowy) – charakteryzował się najbardziej agresywnym spadkiem defektów na wczesnym etapie.

-

N3/N3P (czerwony) – wykazał szybki, ale mniej stabilny spadek.

-

N2 (niebieski) – startuje z wyższego poziomu defektów, ale spadek jest bardzo dynamiczny i dorównuje, a nawet przewyższa poprzedników.

Warto zaznaczyć, że intensywność spadku defektów w procesie N2 jest szczególnie imponująca, biorąc pod uwagę złożoność nowej technologii tranzystorowej GAA, której masowe wdrożenie jest historycznym krokiem w rozwoju całej branży.

Im więcej produktów, tym szybciej uczymy się produkcji

TSMC przypisuje szybkie tempo poprawy gęstości defektów nie tylko postępowi technologicznemu, ale także dużemu wolumenowi produkcyjnemu i różnorodności produktów. Firma zaznacza, że proces N2 już teraz ma więcej tzw. „wyjść taśmowych” (pierwszych egzemplarzy chipów), niż miało to miejsce w przypadku poprzednich procesów. Jest to wynikiem rozpoczęcia produkcji układów zarówno dla klientów z branży smartfonów, jak i wysokowydajnych systemów obliczeniowych (HPC).

Większa liczba projektów korzystających z tego samego procesu technologicznego pozwala szybciej identyfikować i eliminować błędy, co skraca cykle nauki i przekłada się na szybsze dojście do wysokiej wydajności masowej produkcji.

Zgodnie z ujawnionym harmonogramem, TSMC planuje rozpocząć masową produkcję układów w technologii N2 już pod koniec czwartego kwartału 2025 roku. W kontekście prezentowanych danych i tempa spadku defektów wszystko wskazuje na to, że firma dotrzyma tego terminu.

Pokaż / Dodaj komentarze do: TSMC na prostej drodze do ery 2 nm. Dane potwierdzają imponujący postęp w redukcji defektów