Na ostatnim wydarzeniu technologicznym TSMC zaprezentowało nie tylko nowe rozwiązania związane z produkcją półprzewodników, ale również postępy w obszarze zaawansowanych technologii opakowaniowych. W centrum uwagi znalazła się nowa technologia SoW-X, która ma stanowić kolejny kamień milowy w rozwoju wydajności obliczeniowej.

TSMC od lat odgrywa kluczową rolę w przesuwaniu granic możliwości chipów, szczególnie poprzez rozwój technologii takich jak CoWoS (Chip-on-Wafer-on-Substrate). To właśnie zaawansowane pakowanie pozwala firmom takim jak NVIDIA oferować zauważalne wzrosty wydajności mimo wolniejszego tempa miniaturyzacji tranzystorów. CoWoS umożliwia łączenie wielu układów na jednej płytce krzemowej i podłożu, co znacznie zwiększa moc obliczeniową całego systemu.

TSMC stawia na nowoczesne rozwiązania

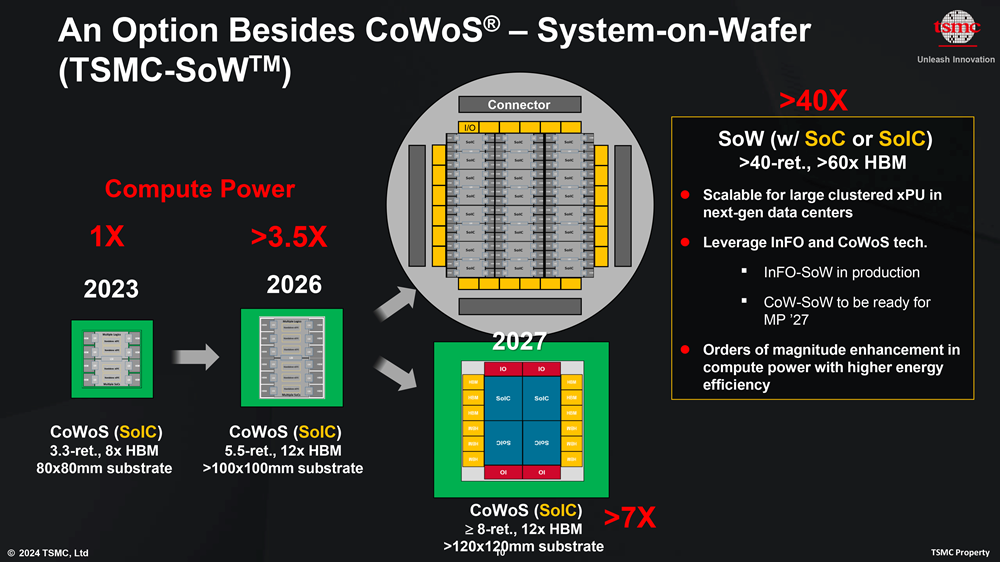

TSMC poinformowało, iż pracuje nad kolejnymi generacjami tej technologii, w tym nad wersjami SoW i SoW-X. Najbliższe wdrożenie ma obejmować wariant CoWoS z reticle size zwiększonym do 9,5x, co pozwoli na zintegrowanie aż 12 stosów pamięci HBM. Dla porównania, obecne rozwiązania, takie jak CoWoS-L, operują na poziomie 5,5x, więc planowany skok to znaczący postęp technologiczny. Produkcja tej wersji ma rozpocząć się do 2027 roku i przewiduje się, że będzie to rozwiązanie szerzej dostępne niż inne alternatywy pojawiające się w tym samym okresie.

Na najnowszym wydarzeniu technologicznym TSMC zaprezentowało nie tylko nowe rozwiązania związane z produkcją półprzewodników, ale również postępy w obszarze zaawansowanych technologii opakowaniowych.

W dłuższej perspektywie TSMC planuje przejście z CoWoS na bardziej zaawansowane rozwiązania SoW (System-on-Wafer), które według zapowiedzi mają oferować aż 40-krotnie większy reticle size i aż 60 stosów HBM. To czyni je idealnymi dla zastosowań AI, szczególnie w dużych klastrach obliczeniowych. Na tym jednak ambicje firmy się nie kończą — nowo zapowiedziany wariant SoW-X ma potencjalnie zapewniać nawet 40 razy większą moc obliczeniową niż obecne rozwiązania CoWoS, choć szczegóły techniczne pozostają jeszcze nieujawnione.

Produkcja na dużą skalę dla pakietów SoW i SoW-X również planowana jest na 2027 rok, co sugeruje, że TSMC zamierza utrzymać swoją dominację w obszarze zaawansowanego pakowania chipów także w kolejnych latach.

Tajwański gigant wyraźnie nie zamierza oddać pola konkurencji i kontynuuje strategię rozwoju, która już teraz zapewnia mu pozycję lidera w tej kluczowej technologicznie dziedzinie.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

TSMC ujawnia SoW-X. Rewolucyjne rozwiązanie ma zapewnić 40x większą moc obliczeniową