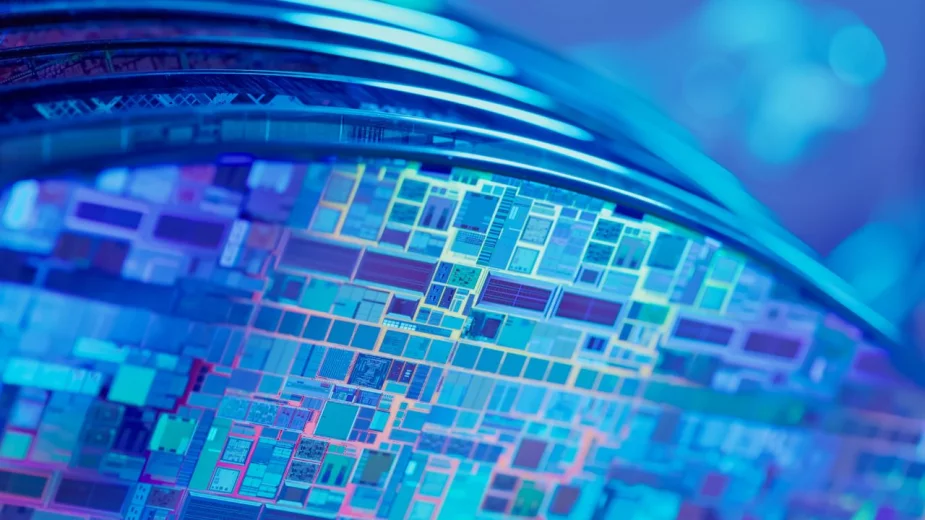

W ciągu najbliższych kilku lat przemysł mikrochipów może zapewnić duży skok w procesach produkcyjnych komponentów krzemowych. TSMC jest bardzo pewne siebie, zapewniając, że dostarczy lepsze litografie od tych opracowanych przez konkurencję.

TSMC jest pewne swego

Oczekuje się, że przyszłe litografie Intela 20A i 18A zadebiutują w nowych procesorach w 2024 lub 2025 roku. Jednak TSMC ogłosiło już zwycięstwo nad amerykańską firmą, planując wprowadzenie porównywalnej technologii produkcyjnej w tych samych ramach czasowych, ale zapewniającej przewagę praktycznie w całym przekroju.

Według TSMC ich 3 nm litografia jest „porównywalna” z technologią 18A od Intela.

Podczas ostatniej prezentacji wyników finansowych dyrektor generalny TSMC, C.C. Wei stwierdził, że ich wewnętrzna ocena potwierdziła udoskonalenia technologii N3P. Proces produkcyjny klasy 3 nm od TSMC wykazał „porównywalny PPA” (obszar wydajności energetycznej) z litografią 18A pd Intela. Oczekuje się, że N3P będzie jeszcze lepszy, a pojawi się wcześniej na rynku, będzie mógł pochwalić się „większą dojrzałością technologiczną” i zaoferuje znaczne oszczędności w ramach kosztów produkcji.

Wei podkreślił, że TSMC nie lekceważy konkurencji. Wspomniał również, że oczekuje się, że jego technologia 2 nanometrów, choć wciąż jest opracowywana, przewyższy zarówno N3P, jak i 18A. Producent wierzy, że jego 2 nm litografia będzie najbardziej zaawansowaną technologią w branży półprzewodników, kiedy zostanie wprowadzona na rynek w 2025 roku.

Nadchodzi rewolucja Gate-All-Around

Spodziewamy się, że Intel wprowadzi na rynek pierwsze procesory wyprodukowane w procesie 20A w 2024 roku, oferując istotny skok w technologii produkcji chipów poprzez implementację wszechstronnych tranzystorów RibbonFET z bramką Gate-All-Around. RibbonFET stanowi pierwszą poważną przebudowę tranzystora od czasu wprowadzenia tranzystorów FinFET w 2011 roku i obejmie nową technologię sieci dostarczania zasilania (BSPDN) znaną jako PowerVia.

Jednocześnie Wei potwierdził, że TSMC będzie w dalszym ciągu korzystać ze sprawdzonej technologii tranzystorów FinFET wraz z tradycyjnymi metodami dostarczania mocy w całej linii 3 nm litografii (N3, N3E, N3P, N3X). Tranzystory typu GAA i BSPDN zostaną wprowadzone w technologiach N2, których masowa produkcja ma nastąpić w drugiej połowie 2025 r.

Wei wspomniał, że oczekuje się, że N3 będzie stanowić „średnio jednocyfrowy procent” całkowitych przychodów TSMC z wafli krzemowych w 2023 r., przy czym w 2024 r. będzie to już znacznie wyższy odsetek. Istnieje duży popyt na produkty wykonane w 3 nm procesie technologicznym ze strony różnych klientów, którzy oczekują lepszej wydajności, efektywności energetycznej, uzysków i „kompleksowej obsługi platform” zarówno dla obliczeń o wysokiej wydajności (HPC), jak i układów do smartfonów.

Pokaż / Dodaj komentarze do: TSMC twierdzi, że ma przewagę technologiczną. Porównuje swoją 3 nm litografię z Intel 18A