Od kilku lat jest bardzo głośno o architekturze RISC-V, która stanowić ma alternatywę dla procesorów x86, a ostatnio pisaliśmy nawet o pierwszym laptopie z procesorem opartym na otwartym kodzie źródłowym RISC-V ISA. Tym razem zaś startup Ventana Microsystems zaprezentował swój pierwszy procesor serwerowy — Veyron V1 — wykorzystujący architekturę RISC-V i zaawansowaną 5 nm litografię. Ten serwerowy procesor konkurować ma z układami AMD EPYC i Intel Xeon.

Architektura RISC-V jest stosowana głównie na rynku przemysłowym lub IoT (Internet of Things) ze względu na jej zdolność do oferowania efektywnego wykorzystania energii, możliwości open source, najnowocześniejszych instrukcji i skalowalności sprzętu. Sensowne byłoby rozgałęzienie jej technologii na większą skalę, włączając w to serwery i centra danych, które odgrywają coraz większą rolę we współczesnym świecie. Na taki pomysł wpadło właśnie Ventana Microsystems.

Ventana Microsystems zaprezentowało swoje pierwsze serwerowy CPU, wykorzystujące architekturę RISC-V i 5 nm litografię.

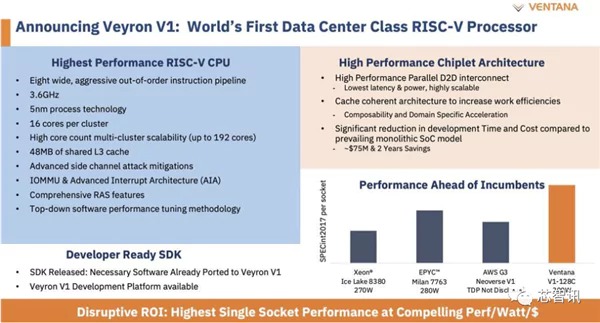

Układ Veyron V1 oferuje rdzeń RISC-V produkowany w 5 nm litografii. Chip zapewnia konstrukcję z ośmioma potokami, częstotliwości do 3,6 GHz i 16 rdzeni na klaster, co daje łącznie 192 rdzenie. Ma również pamięć podręczną L3 o pojemności 48 MB, może obsługiwać „wykonywanie poza kolejnością” i zapewnia zaawansowane zabezpieczenia, w tym blokujące ataki side-channel. Na pokładzie znajdziemy także technologie IOMMU i AIA, funkcjonalności RAS i możliwość regulacji wydajności za pomocą oprogramowania top-down.

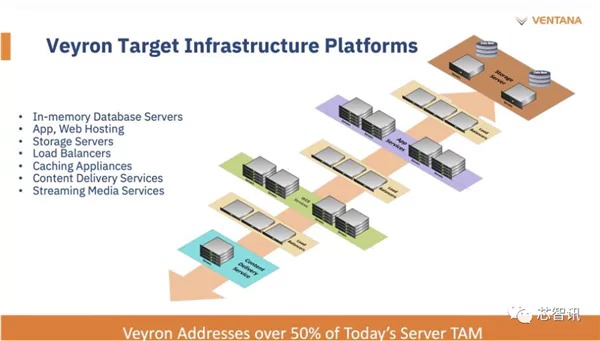

Najważniejszym elementem Veyron V1 wydaje się jednak możliwość wykorzystania CPU w większej liczbie produktów i usług. Jak widać, producent ma nadzieję wykorzystać układ V1 w wielu różnych zadaniach serwerowych do magazynowania danych, web hostingu, centrów danych i usług przesyłania strumieniowego.

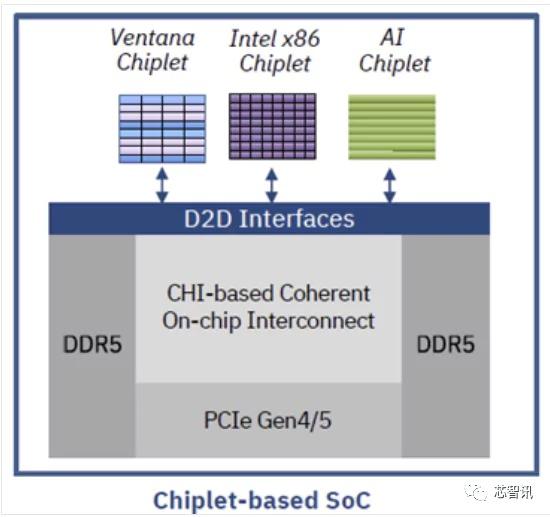

Ogólna konstrukcja chipa ma podobną strukturę jak nowe procesory EPYC firmy AMD, z interfejsami danych po jednej stronie chipa, pamięcią po obu stronach i PCIe Gen5 (z kompatybilnością wsteczną z Gen4). Interfejs Die-to-Die (D2D) jest zgodny z Harness of Wire (HoW) i Universal Chiplet Interconnect Express (UCIe), które są również obsługiwane przez większe firmy, takie jak AMD, Intel, NVIDIA i Arm, a także wiele innych.

Co na to konkurencja? Z jednej strony Drew Henry, wiceprezes wykonawczy ds. strategii i marketingu w firmie ARM, stwierdził, że cieszy się z większej konkurencji na rynku i faktu, że w tym segmencie pojawiają się nowi gracze. Z drugiej strony kierownictwo ARM mówi: „Szanujemy RISC-V, ale to jeszcze nie jest konkurencja”. Czas pokaże.

Spodobało Ci się? Podziel się ze znajomymi!

Pokaż / Dodaj komentarze do:

Zapowiedziano pierwszy serwerowy procesor RISC-V. Nawet 192 rdzenie produkowane w 5 nm